ARM 处理器

计算机结构

| Bus | 总线,在module之间传输数据 |

|---|---|

| Port | 端口,I/O的实体设备 |

| Device Driver | 驱动I/O设备的软件(硬件设备的软件界面) |

| Interface | 软件是Device Driver, 硬件是I/O + 外部设备 |

| Memory | |

| CPU |

指令集结构

- Low-level Programming

名称

-

Advanced RISC Machine

-

RISC = Reduced Instruction Set Computer

-

CISC = Complex Instruction Set Computer

比较

| RISC | CISC |

|---|---|

| 指令多 | 指令少 |

| 更多编译器 | 更多微指令 |

| 更多寄存器 | 更少寄存器 |

ARM vs. MIPS

| ARM | MIPS |

|---|---|

| 16个寄存器 | 32个寄存器 |

| 更高效,支持64位数据线 | |

| ARM的指令集不一样 |

- 结论:ARM比MIPS更NB!

嵌入式编程语言

常见语言

- C, C++, Python, Java, MicroPython

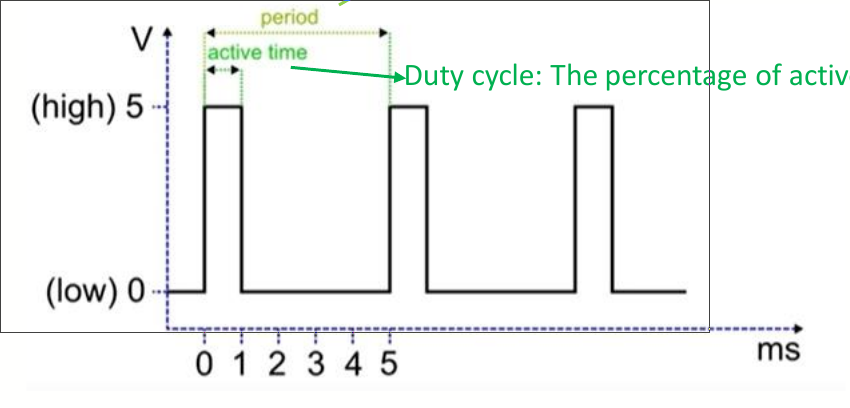

PWM - Pulse Width Modulation

原理

- 用数字源产生模拟信号

图像分析

$$ Duty \ Cycle = \frac{Active \ time}{T} \times 100% \\\ \\ Average \ Time = high \cdot Duty \ Cycle / 100% $$

串行通信的方式

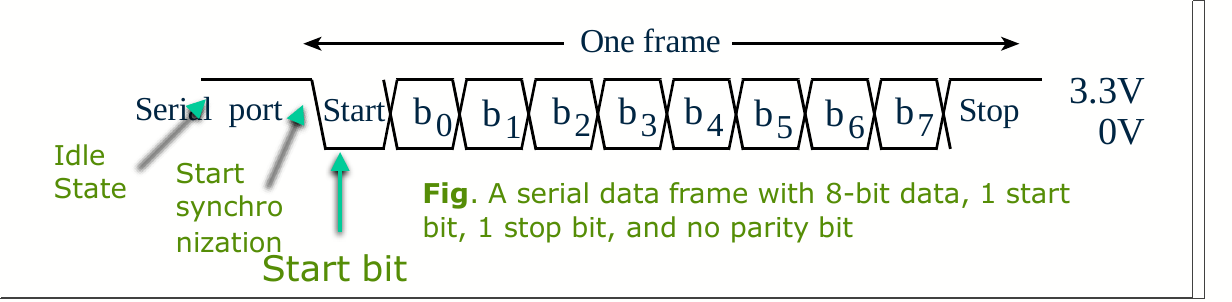

UART – Universal Asynchronous Reception and Transmission

- 部件与原理

-

RX - Receiver

-

TX - Transmitter

-

Protocal - 总线异步通信系统协议

- 工作原理

-

Start Bit $0$ $\longrightarrow$ Stop Bit $1$

-

Data Length

- 理想状态下,串行线为$1$

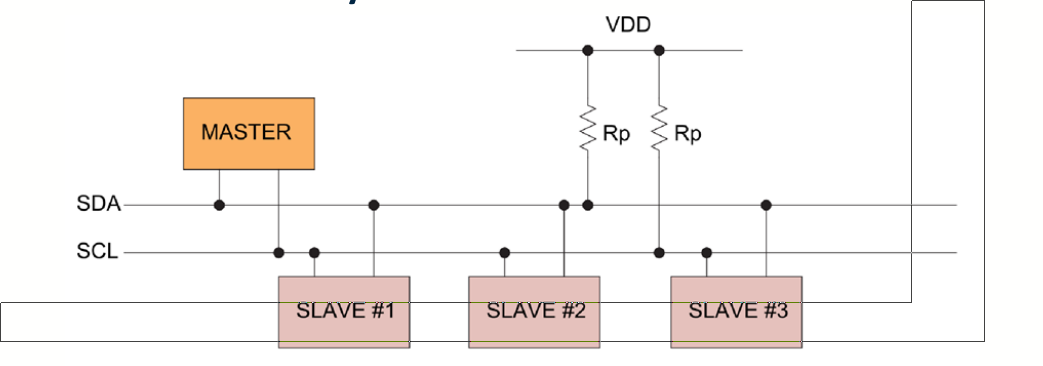

I2C - Inter-Integrated-Circuit

- 部件与原理

-

一主机,多从机

-

只有主机可以初始化传输数据

-

总线系统同步通信的协议

-

SDA - Serial Data Line: 传输数据、地址、控制信号

-

SCL - Serial Clock Line:用于同步

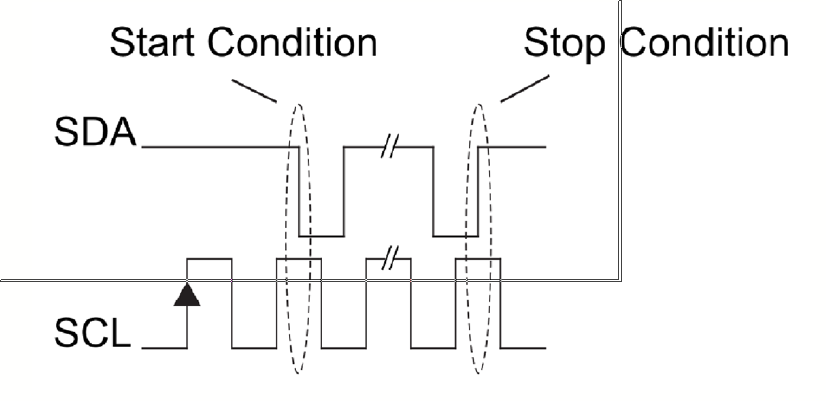

- 工作原理

-

Data Length: 8-bit

-

Start (Stop) Condition

- 地址字节(8位)

-

前7位构成从机地址

-

最后1位作为读/写指令

- 0是写入(从机)

- 1是读取

- 确认位和非确认位(ACB/NACB)

-

每字节数据输入成功,接受者返回ACB;失败返回NACB

-

在SCL为High时,保持SDA为low,以此产生ACB

- 数据位

-

8位字节格式

-

以地址字节开头,每个地址字节后必须跟着一个ACB/NACB

-

必须在SCL保持high时才能发送和接收数据

-

SCL保持低位时可以操作数据线

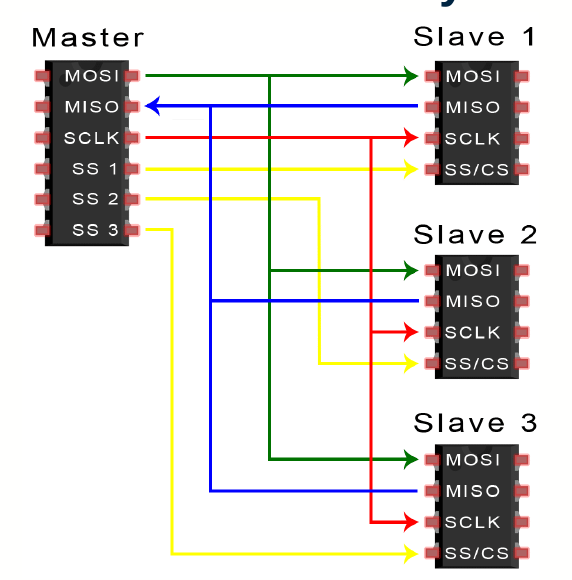

SPI - Serial Peripheral Interface

- 部件与协议

-

总线系统的串行通信协议

-

一主机,(一)多从机

-

全双工

-

主从层次结构

- 结构

- SS(CS): Slave Select (Chip Select),从机并行连接,处于low位时被激活

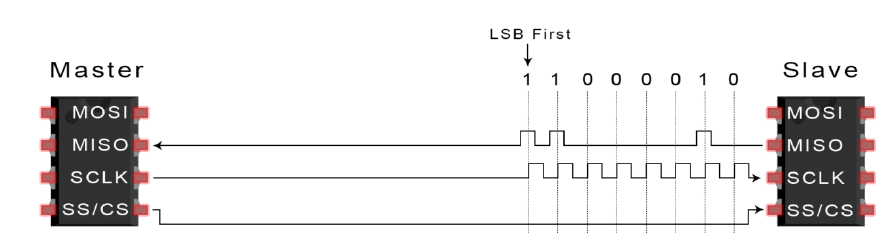

- 原理

stateDiagram

主机向从机发送时钟信号 --> 将对应从机的SS/CS调成low

将对应从机的SS/CS调成low --> MOSI发送数据

MOSI发送数据 --> MISO接受从机发回的数据: 如果有必要的话

- 时钟参数

| Bit | CPOL(Clock Polarity) | CPHA(Clock Phase) |

|---|---|---|

| 0 | Idle State = 0 | In Phase |

| 1 | Idle State = 1 | Out of Phase |

对比

| 比较项目 | UART | I2C | SPI |

|---|---|---|---|

| Communication Type | Serial | Serial/Parallel (multi-master, one at a time) | Serial (single-master) |

| Number of Wires Required | Minimum of two (TX and RX) | Two wires (SDA and SCL) plus optional ground wire | Minimum of three (MOSI, MISO, and CLK) plus optional slave select wire(s) |

| Data Transfer Speed | Typically up to several Mbps | Typically up to several hundred Kbps | Typically up to tens of Mbps |

| Maximum Distance Supported | Up to a few meters | Up to several meters | Up to several meters |

| Simplicity | Simple | Simple | Relatively Complex |

| 工作方式 | 异步 | Half-duplex | Full-duplex |