ADC & DAC

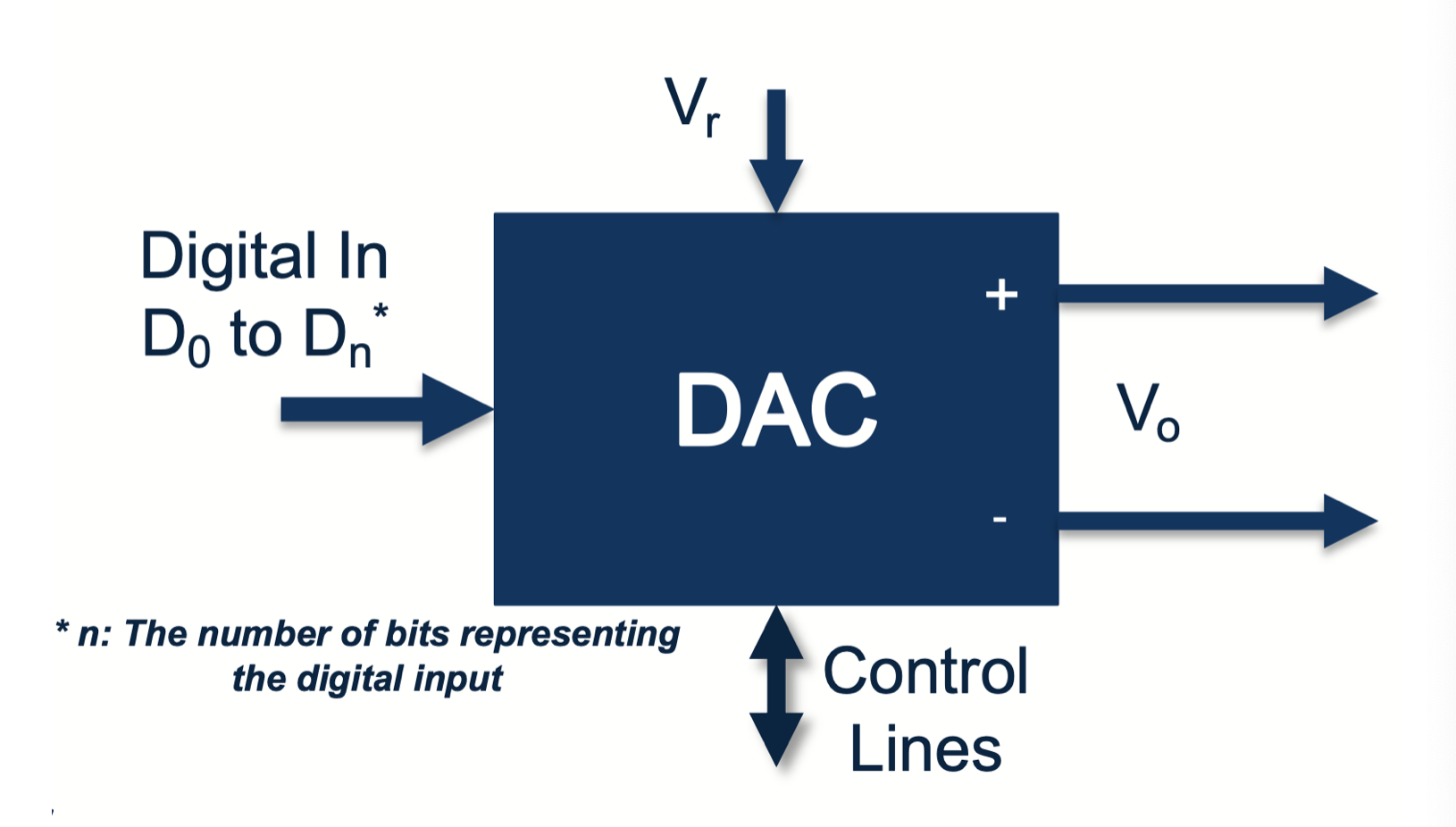

DAC

I/O和解释

$$ \begin{gather} \begin{aligned} V_o &= \frac{ D }{ 2^n } V_r \end{aligned} \end{gather} $$

重要类型 - R-2R Ladder DAC

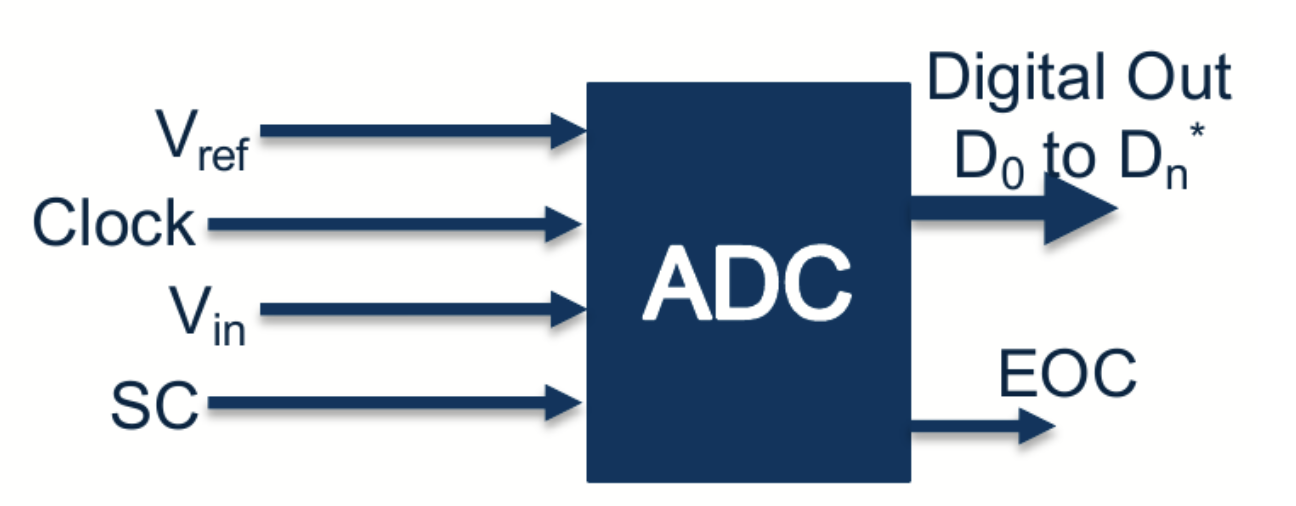

ADC

I/O和原理

| Category | Concept |

|---|---|

| $V_{ref}$ | Reference Voltage |

| Resolution(LSB) | $\dfrac{ V_r }{ 2^n }$ |

| SC | Start of Conversion |

| EOC | End of Conversion |

| $D_i$ | 数字输入的二进制第$i$位 |

$$ \begin{gather} \begin{aligned} D &= \frac{ V_i }{ V_r } 2^n \end{aligned} \end{gather} $$

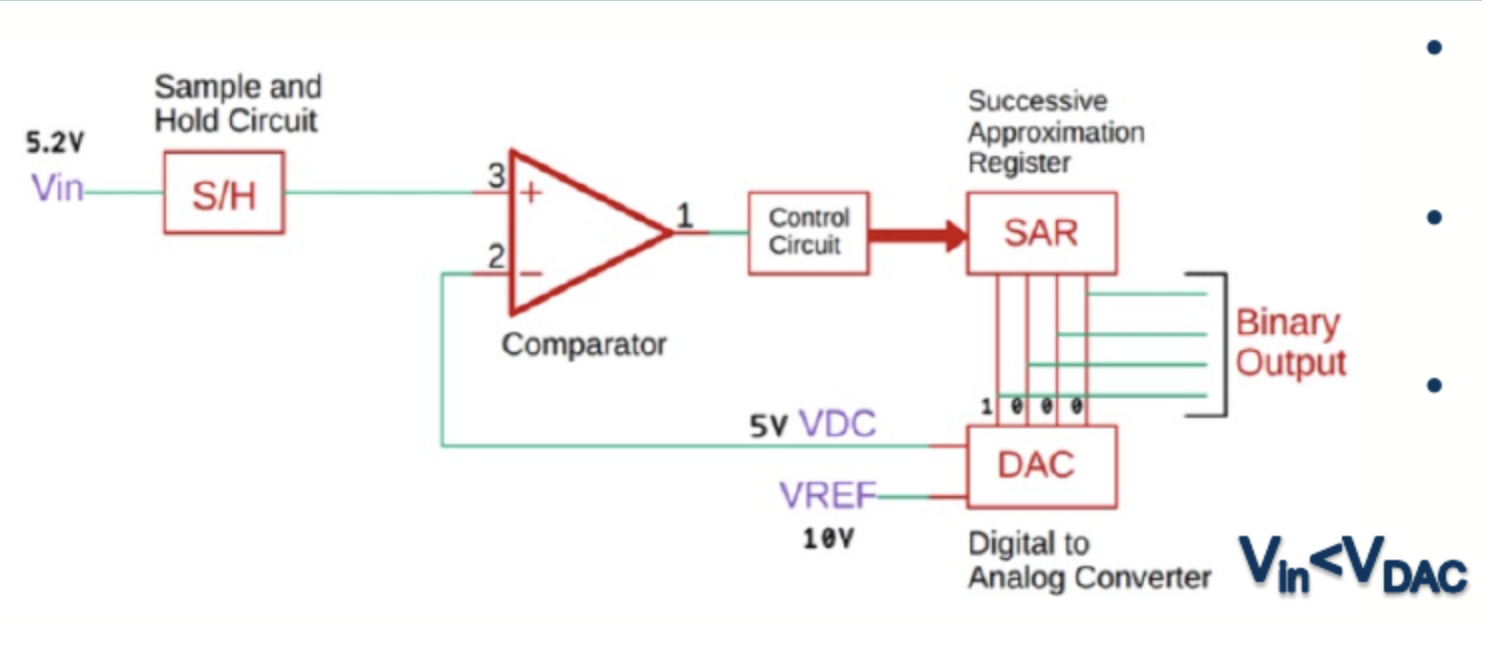

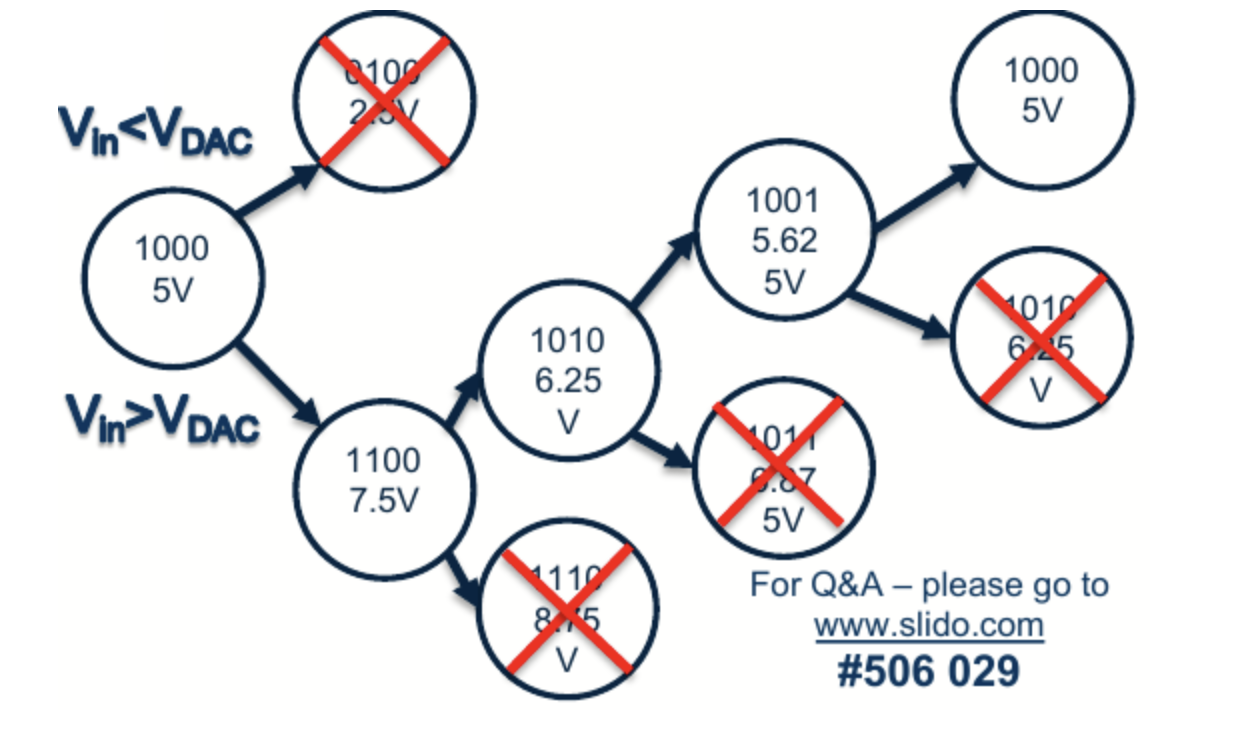

Successive Approximation ADC

总结

$$ \begin{gather} \begin{aligned} 数字输入 \times 分辨率 &= 模拟输出 模拟输入 % 分辨率 &= 数字输出 \end{aligned} \end{gather} $$

Opamp Revision

Imperfection in Opamp

- Ideal Opamp + Current Sources = Model of a Real Opamp

Bias Current

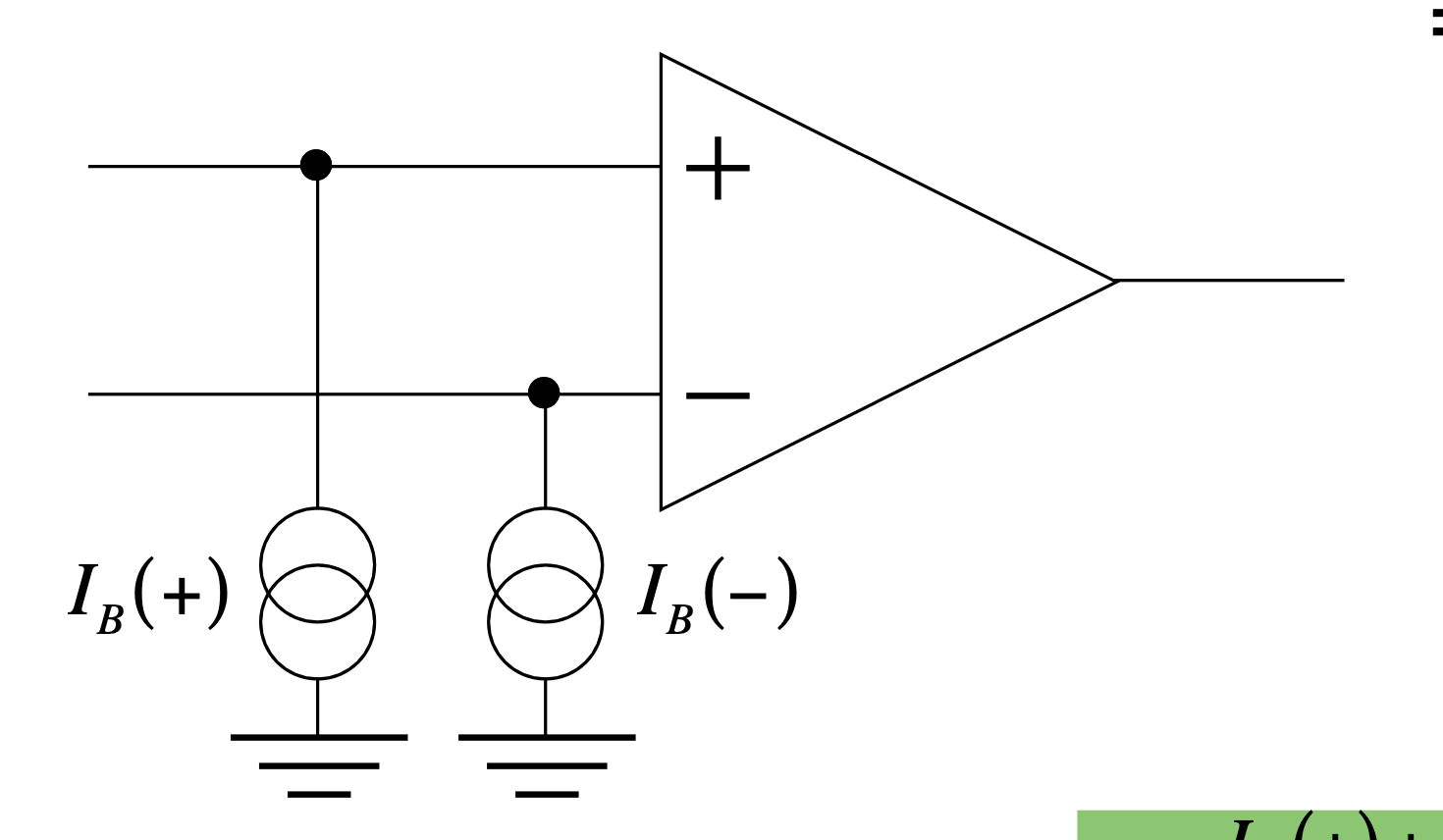

定义

- 图中的的放大器是理想的

$$ \begin{gather} \begin{aligned} I_B(+) &\approx I_B(-) \ I_B &= \frac{ I_B(+) + I_B(-) }{ 2 } \end{aligned} \end{gather} $$

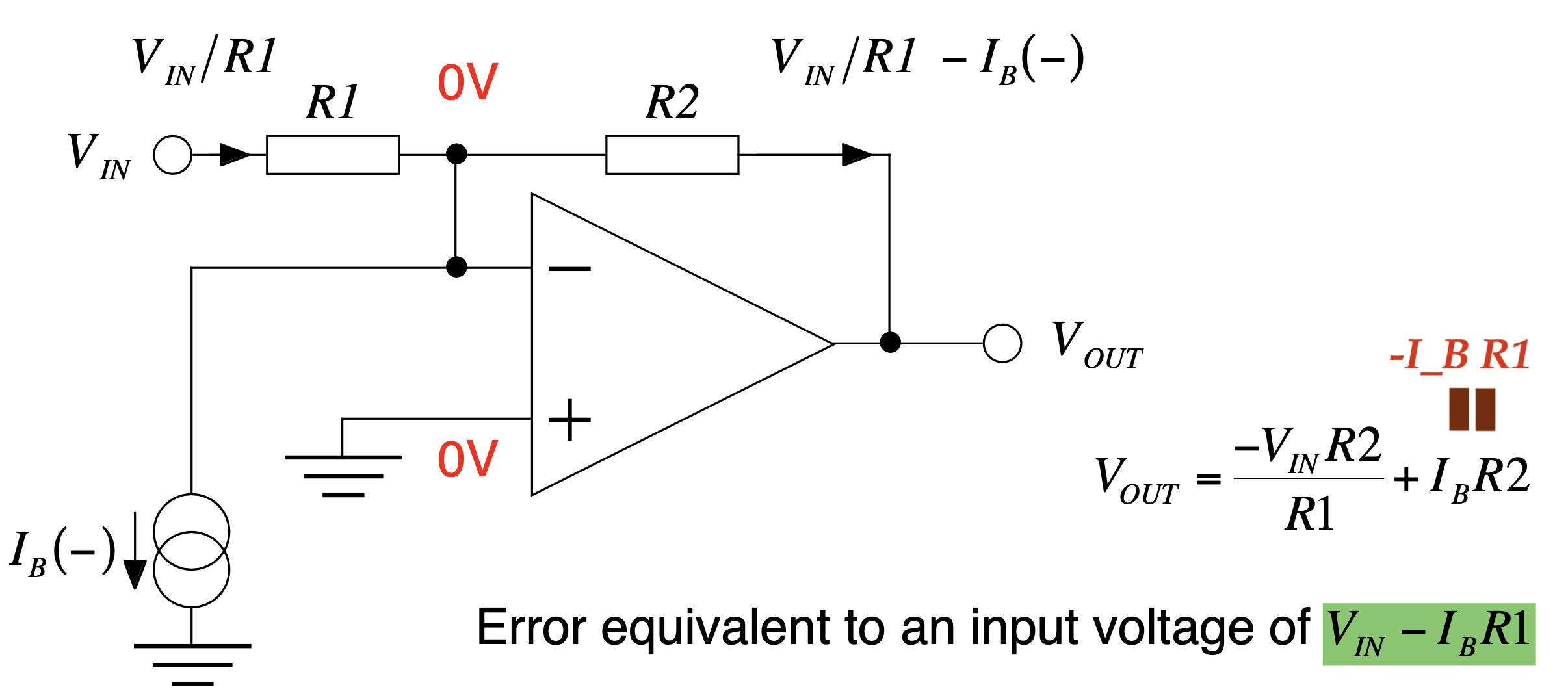

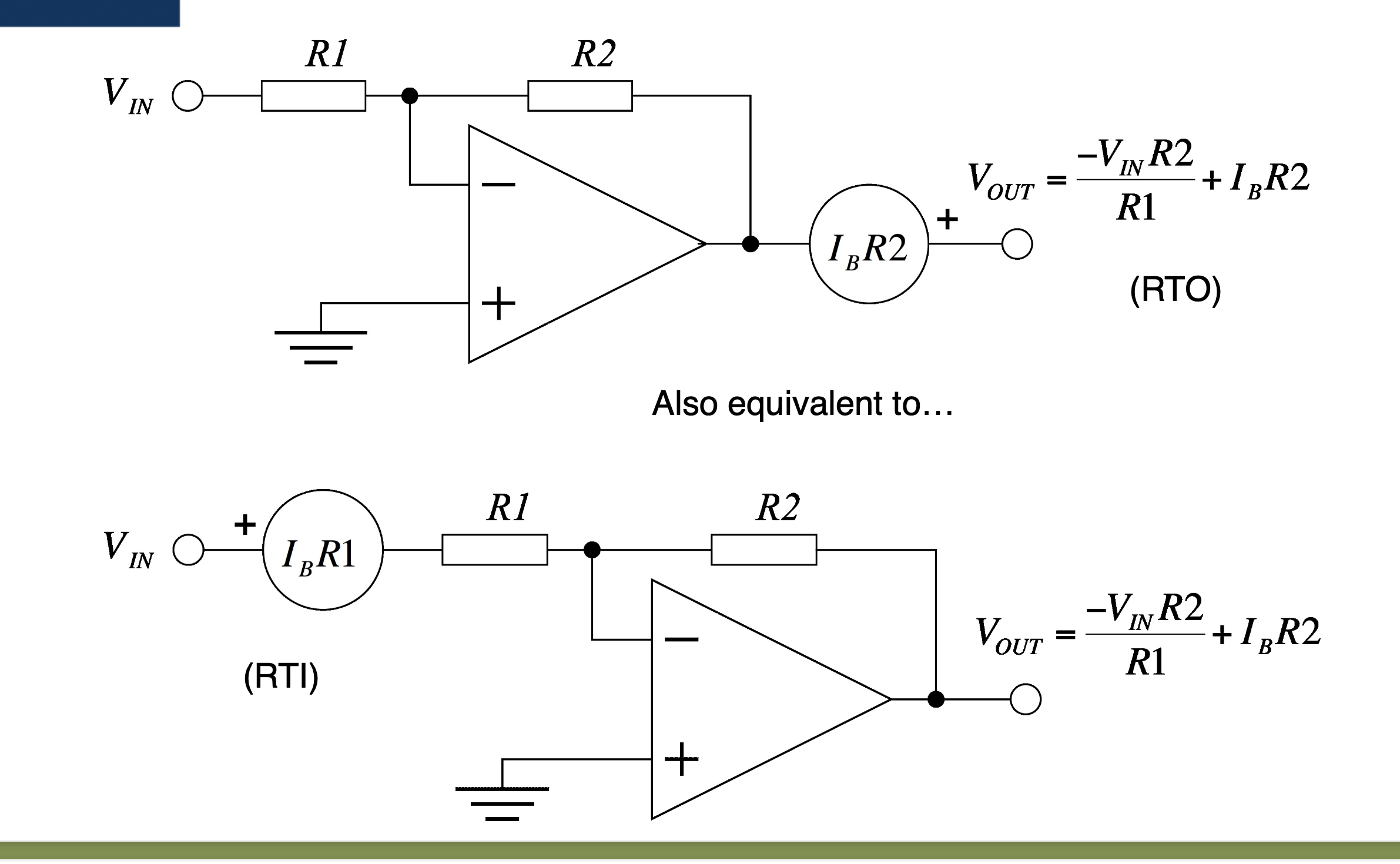

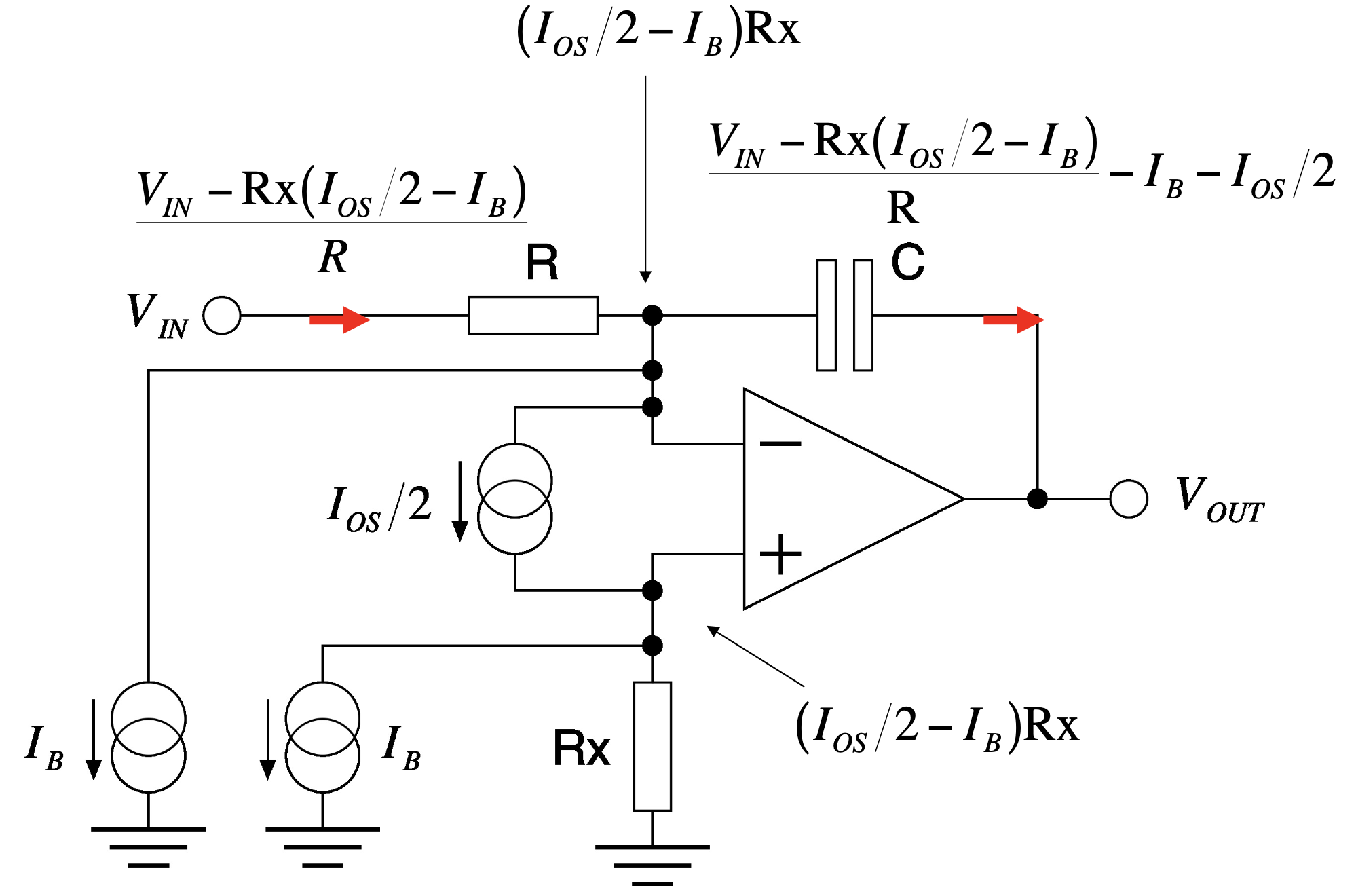

以Inverting Configuration 为例介绍非理想时的输出电压

$$ \begin{gather} \begin{aligned} V_o &= - \frac{ V_{in} R_2 }{ R_1 } + I_B R_2 \\ &= -\frac{ V_{in} R_2 }{ R_1 } - I_B R_1 \end{aligned} \end{gather} $$

| Category | Concept |

|---|---|

| Refer to Output(RTO) | $I_BR_2$ |

| Refer to Input(RTI) | $-I_BR_1$ |

- 等效电路

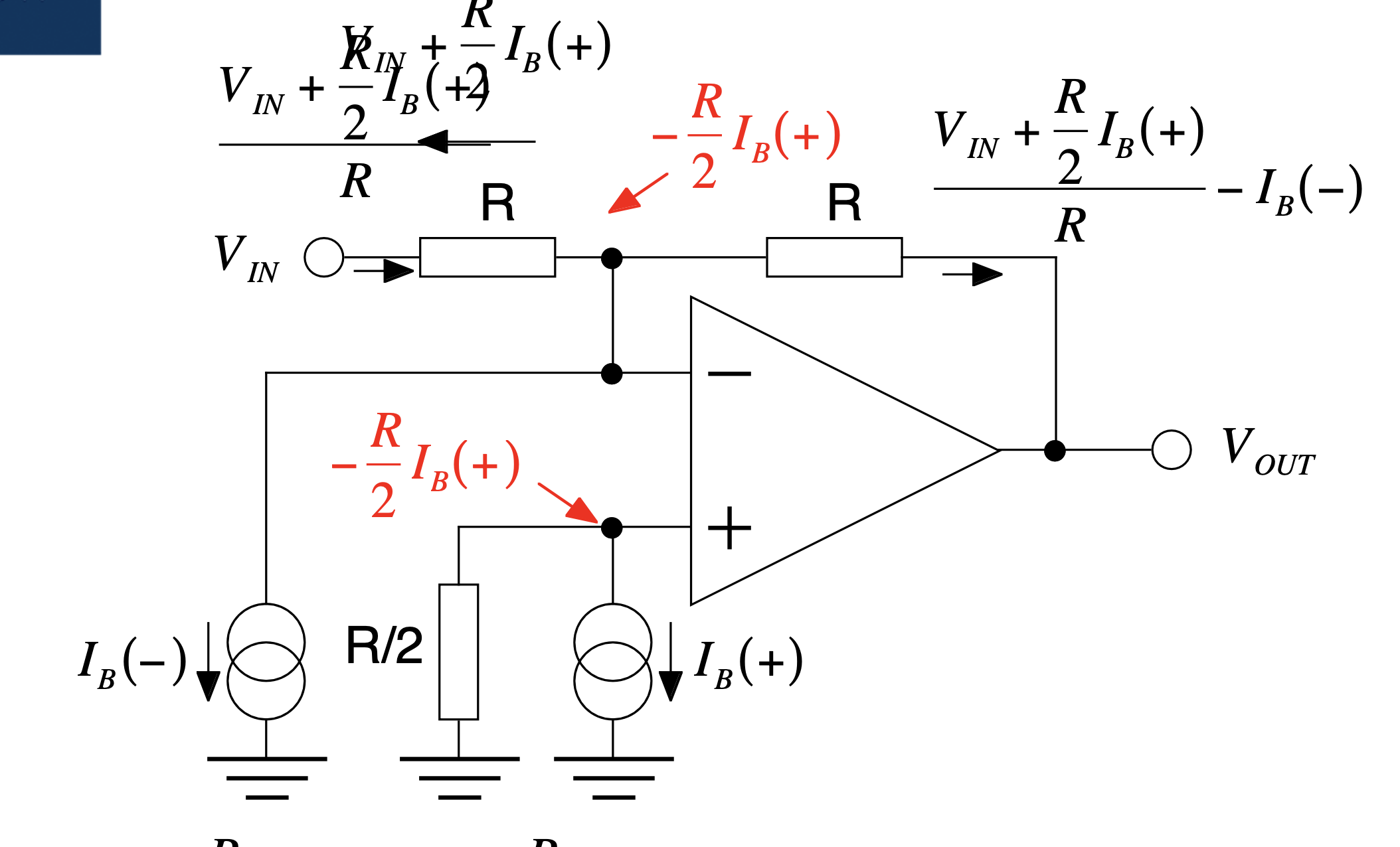

Compensation

$$ \begin{gather} \begin{aligned} V_o &= -V_{in} + R(I_B(-) - I_B(+)) \\ &= -V_{in} + RI_{os} \end{aligned} \end{gather} $$

Input Offset Current

Definition

$$ \begin{gather} \begin{aligned} I_{os} &= |I_B(+) - I_B(-)| \end{aligned} \end{gather} $$

用Bias 和 Offset Current 来表示电流

$$ \begin{gather} \begin{aligned} I_B(+) &= \frac{ I_{os} }{ 2 } + I_B \\ I_B(-) &= - \frac{ I_{os} }{ 2 } + I_B \end{aligned} \end{gather} $$

Ex. Integrator

$$ \begin{gather} \begin{aligned} V_{out} &= \end{aligned} \end{gather} $$

Figure of Merit

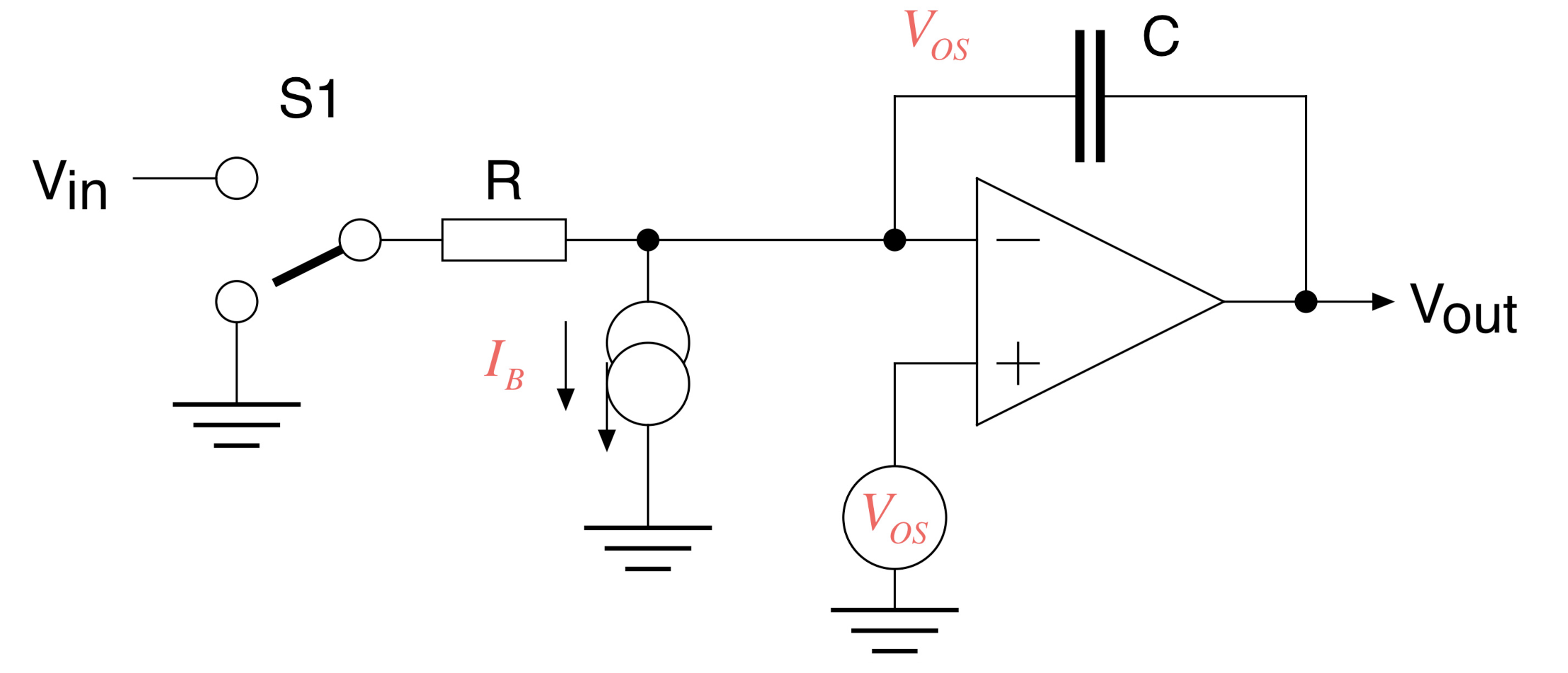

Ex.1 - Integrate and Hold

电路

$S_1$接$V_{in}$时 Integrator

$$ \begin{gather} \begin{aligned} V_{out} &= - \int_{}^{ } \frac{ V_{in} }{ RC }dt \end{aligned} \end{gather} $$

$S_1$接地时 Memory

$$ \begin{gather} \begin{aligned} V_{out} &= Constant \\ | \frac{ dV_{out} }{ dt }| &= \frac{ 1 }{ C } \frac{ dQ }{ dt } \\ &= \frac{ 1 }{ C } (I_B + \frac{ V_{os} }{ R }) \\ &= \frac{ 1 }{ \tau } (V_{os} + I_BR) \end{aligned} \end{gather} $$

- 为了使得$| \dfrac{ dV_{out} }{ dt}|$尽可能小; $V_{out}$不变时,$V_{in}$ 尽可能大

$$ \begin{gather} \begin{aligned} R \ge 2 k \Omega \end{aligned} \end{gather} $$

Figure of Merit

$$ \begin{gather} \begin{aligned} F &= V_{os} + I_{os} R \end{aligned} \end{gather} $$

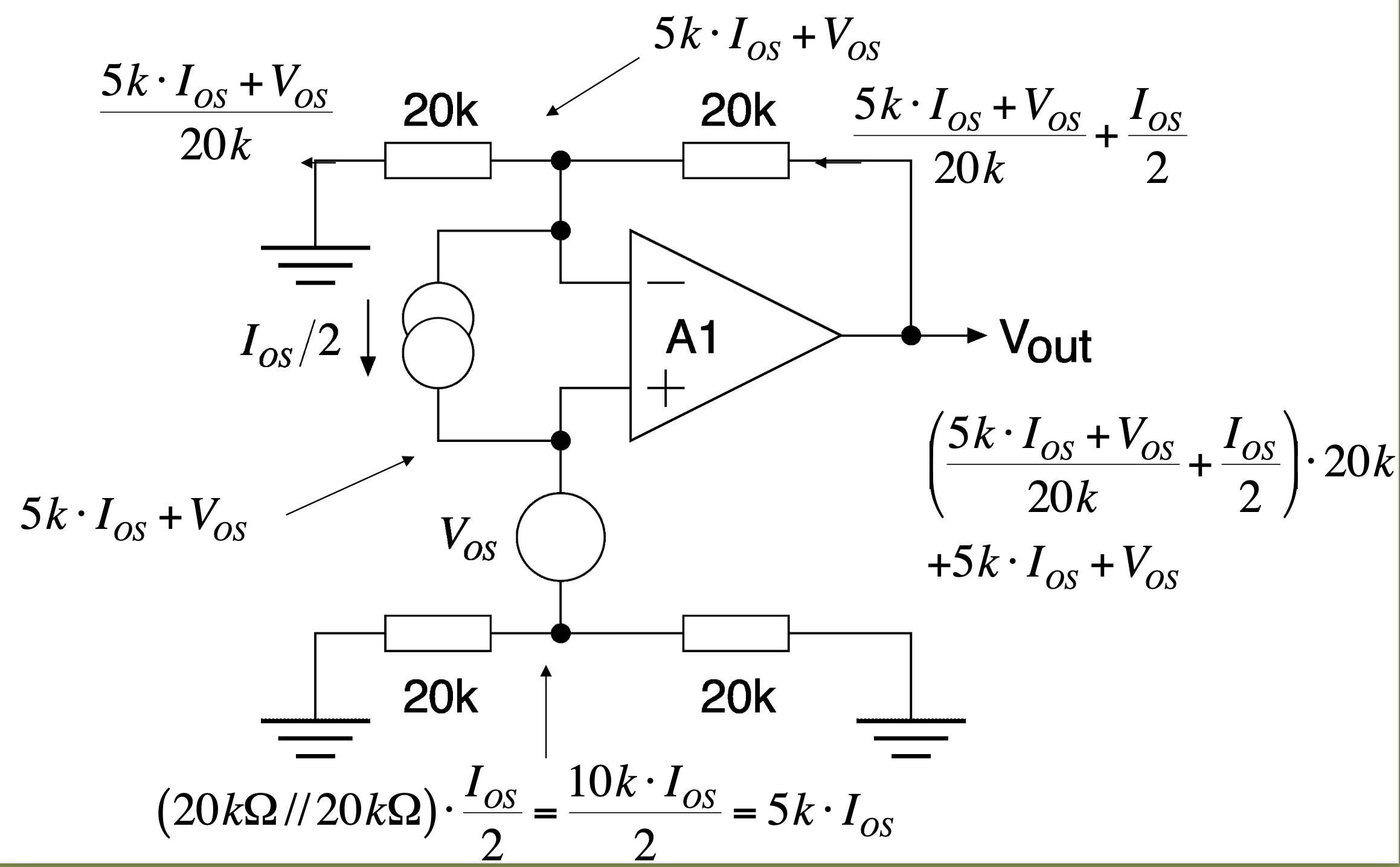

Ex.2 - Differential Amplifier

$$ \begin{gather} \begin{aligned} V_{out} &= 2 V_{os} + 20k \cdot I_{os} \\ F &= 2 V_{os} + 20k \cdot I_{os} \end{aligned} \end{gather} $$

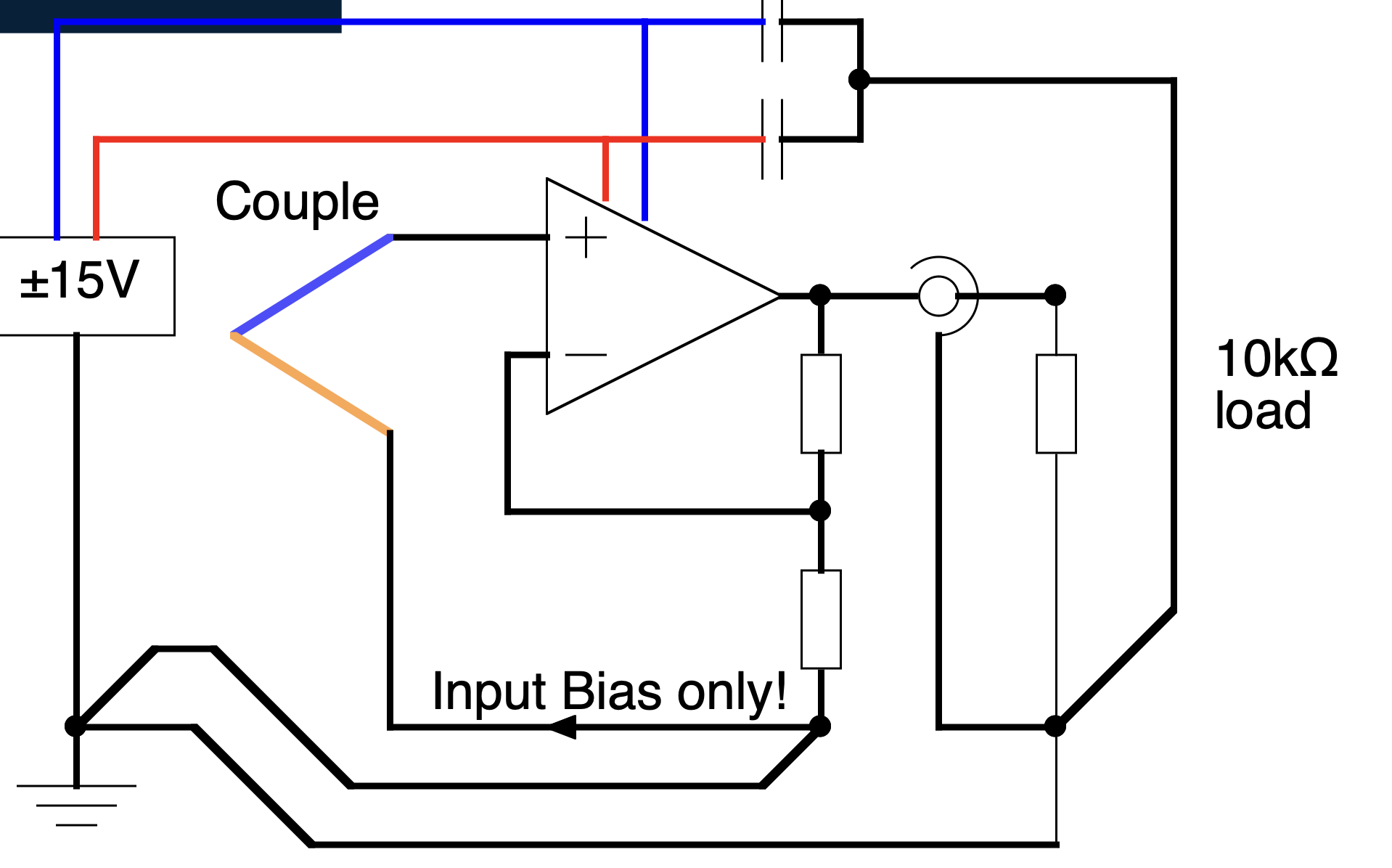

Grounding & Common-Mode Rejection

Power Dissipation Capacitance for CMOS Logic Current

$$ \begin{gather} \begin{aligned} C_{PD} &= \frac{ Q_{switch} }{ V_{CC} } \\ &= \frac{ I_{max} \tau_{switch} }{ V_{CC} } \\ &= \frac{ \tau_{switch} }{ R_{switch} } \end{aligned} \end{gather} $$

Designing Ground

CM Rejection

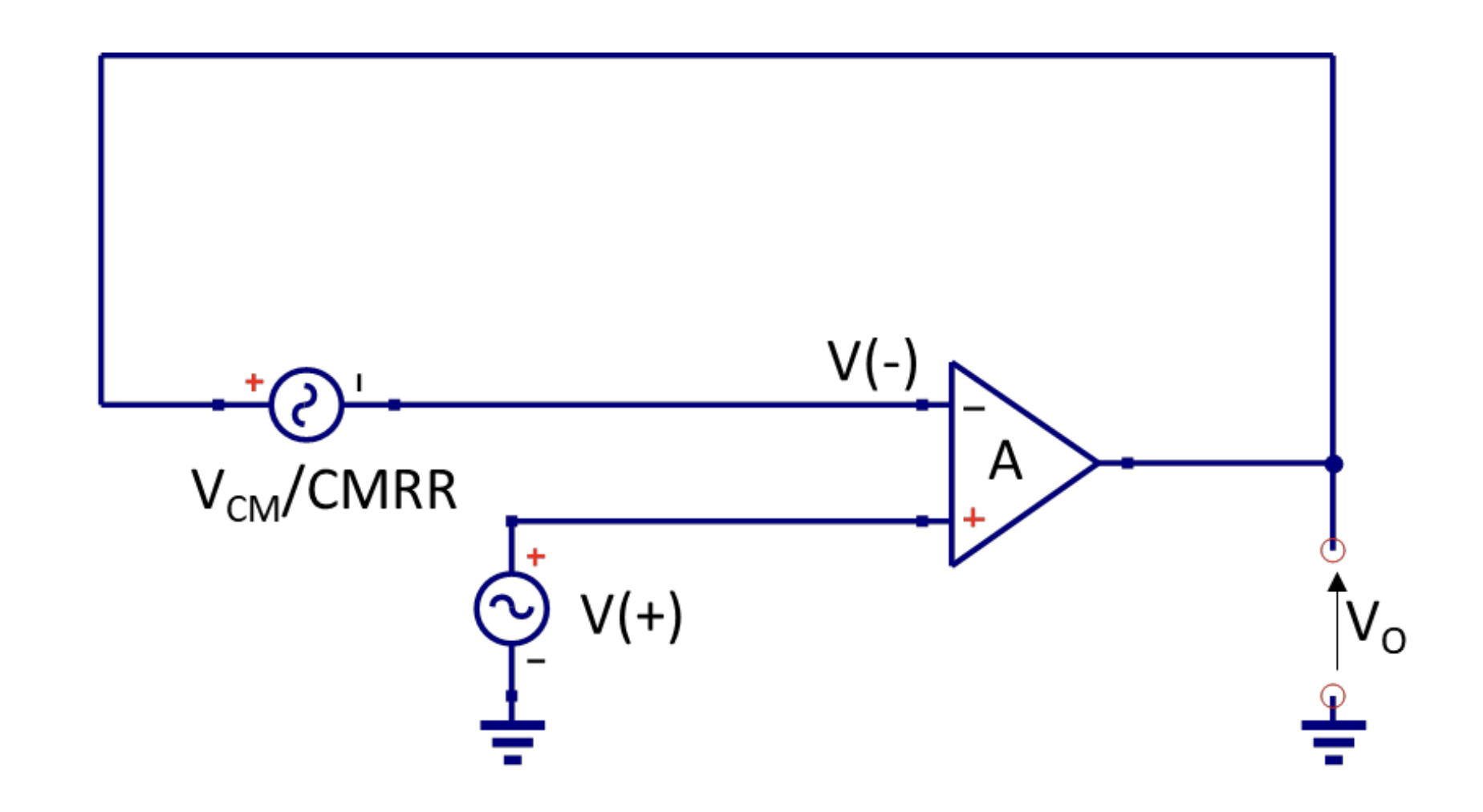

定义

$$ \begin{gather} \begin{aligned} CMRR &= | \frac{ A_{dm} }{ A_{cm} }| \end{aligned} \end{gather} $$

Influence on Error

RTI

$$ \begin{gather} \begin{aligned} V_o &= A_{cm} V_{cm} + A_{dm} V_{diff} \\ &= A_{dm} \Big( V_{diff} + V_{cm} \frac{ A_{cm} }{ A_{dm} }\Big) \\ &= A_{dm} (V_{diff} + \frac{ V_{cm} }{ CMRR }) \\ RTI &= \frac{ V_{cm} }{ CMRR } \end{aligned} \end{gather} $$

等效电路和分析

$$ \begin{gather} \begin{aligned} V_o &= A(V(+) - V(-)) \\ &= A(V(+) - (V_o \pm \frac{ V_{CM} }{ CMRR })) \\ \frac{ V_o }{ V(+) } &= \frac{ A \Big[ 1 + \dfrac{ 1 }{ CMRR } \Big] }{ 1 + A } \\ & \approx 1 + \frac{ 1 }{ CMRR } \end{aligned} \end{gather} $$

- $CMRR$越大,Error越小

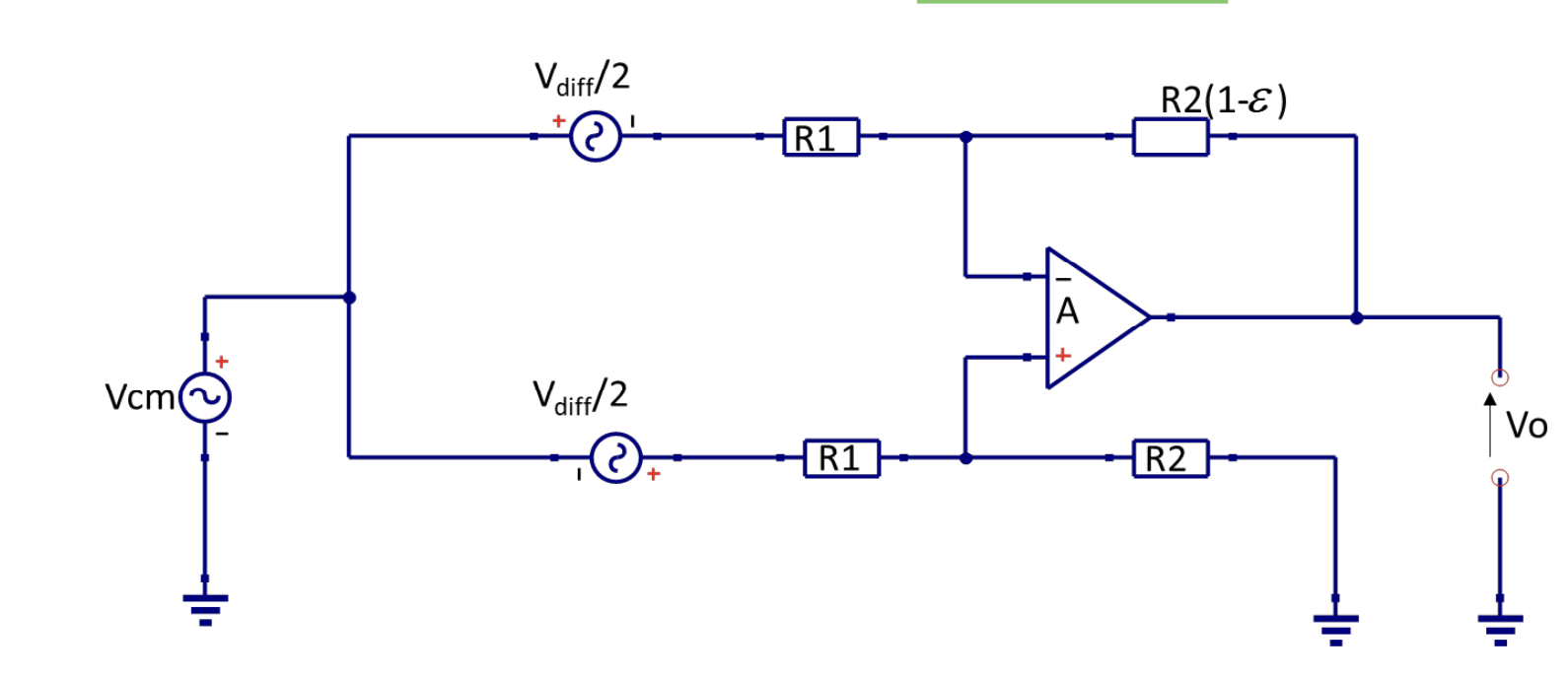

CMRR of Differential Amplifier with Imbalanced Resistors

Gains

$$ \begin{gather} \begin{aligned} V_o &= \frac{ V_{CM} - \dfrac{ V_{diff} }{ 2 } - \dfrac{ R_2 }{ R_1 + R_2 } (V_{CM} + \dfrac{ V_{diff} }{ 2 })}{ R_1 } R_2(1 - \varepsilon) + \frac{ R_2 }{ R_1 +R_2 } (V_{CM} - \frac{ V_{diff} }{ 2 }) \\ &= A_{dm} V_{dm}+ A_{cm} V_{cm} \\ A_{diff} &= \frac{ R_2 }{ R_1 } \Big( 1 - \frac{ R_1 + 2R_2 }{R_1 + R_2 } \times \frac{ \varepsilon }{ 2 }\Big) \\ A_{dm} &= \frac{ R_2 }{ R_1 + R_2 } \varepsilon \end{aligned} \end{gather} $$

CMRR when $\varepsilon$ is Small

$$ \begin{gather} \begin{aligned} CMR(dB) &= 20 l \Big[ \frac{ 1 + \dfrac{ R_2 }{ R_1 } }{ \varepsilon} \Big] \end{aligned} \end{gather} $$

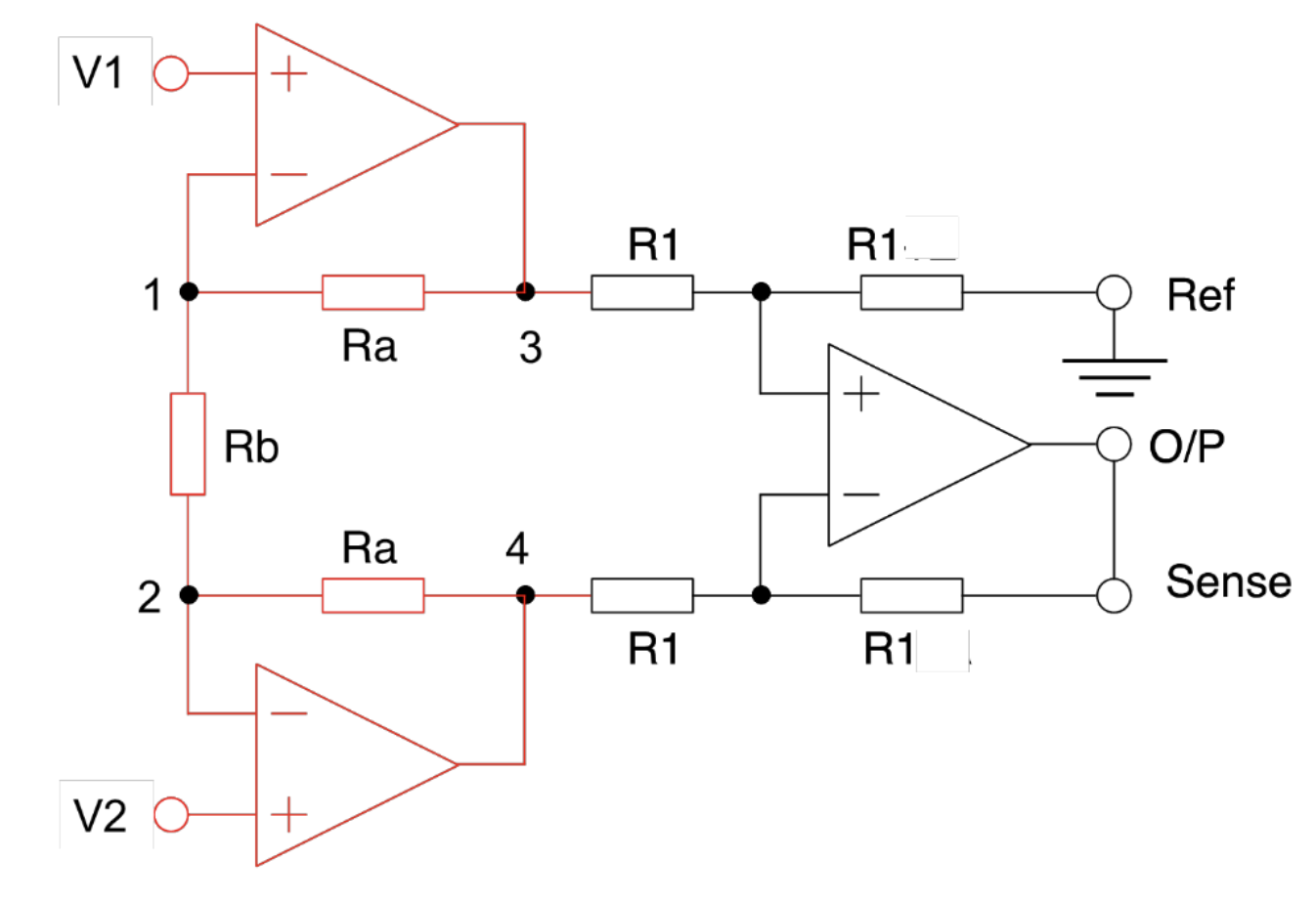

Instrumentaiton Amplifier

电路

-

红色部分是Buffer Stage

-

第二部分是Unity Gain Amplifier

-

电流$I$方向是3-1-2-4, 因此$V_3 - V_1 = V_4 - V_2$

电流/电压 分析

$$ \begin{gather} \begin{aligned} I &= \frac{ V_3 - V_4 }{ 2R_a + R_b } \\ &= \frac{ V_1 - V_2 }{ R_b } \\ V_o &= V_3 - V_4 \\ &= (V_1 - V_2) \frac{ 2R_a + R_b }{ R_b } \end{aligned} \end{gather} $$

Gain & CMRR Considering $\varepsilon$

$$ \begin{gather} \begin{aligned} A_{diff} &= \frac{ 2R_a + R_b }{ R_b } \\ A_{cm} &= \frac{ \varepsilon }{ 2 } \\ CMRR &= \frac{ 4R_a +2R_b }{ \varepsilon R_b } \end{aligned} \end{gather} $$

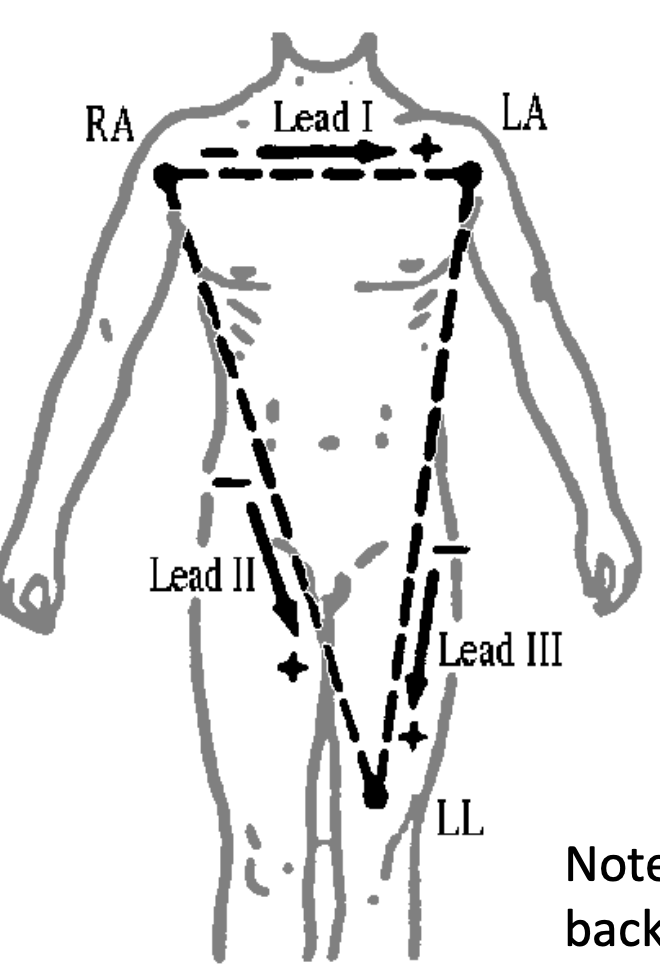

IA Application (ECG)

测量方法

| Category | Concept |

|---|---|

| LL-RA | |

| LL-LA | |

| LA-RA |

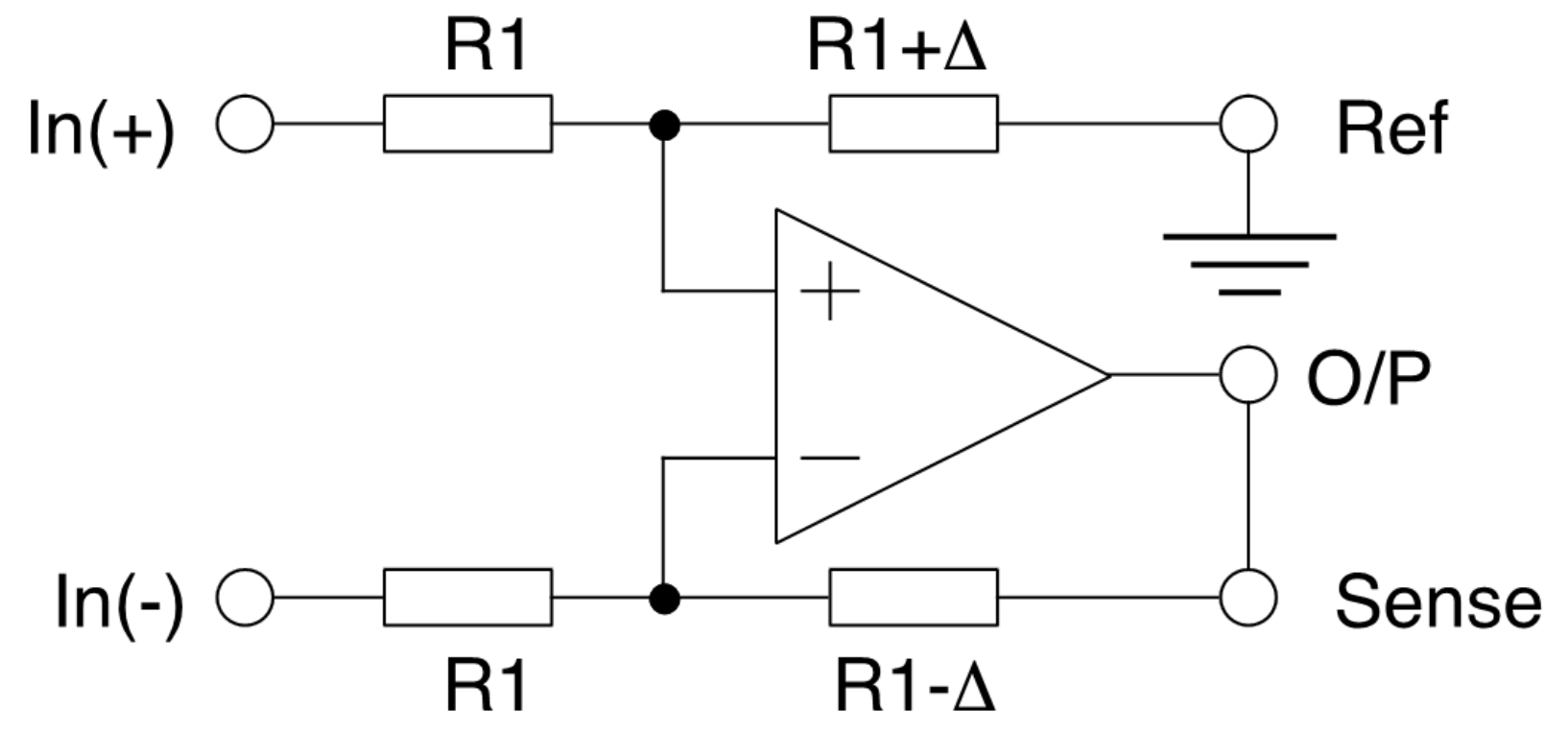

Difference Amplifier Problem

Circuit

$$ \begin{gather} \begin{aligned} \Delta &\ll R_1 \\ Sense &= O/P \\ &= \Big( In(+) - In(-) \Big) + Ref \\ G &= 1 \\ Ref &= 0V \end{aligned} \end{gather} $$

DM Gain

- $In(+) = V_{diff} = -In(-)$

$$ \begin{gather} \begin{aligned} A_{dm} &\approx 1 \end{aligned} \end{gather} $$

$$ \begin{gather} \begin{aligned} V_p &= V_n \\ (Ref - In(+)) \frac{ R_1 }{ R_1 + R_1 + \Delta } &= (Sense - In(-)) \frac{ R_1 }{ R1 + R_1 - \Delta } \\ V_{diff} &= Sense - Ref \end{aligned} \end{gather} $$

CM Gain

- $In(+) = In(-) = V_{CM}$

$$ \begin{gather} \begin{aligned} (Ref- V_{CM}) \frac{ R_1 }{ 2R_1 + \Delta} &= (Sense -V_{CM}) \frac{ R_1 }{ 2R_1 - \Delta } \\ (Ref -V_{CM}) (2R_1 - \Delta) &= (Sense - V_{CM}) (2R_1 + \Delta)) \\ A_{CM} &= \frac{ Sense - Ref }{ V_{CM} } \\ & \approx \frac{ \Delta }{ R_1 } \end{aligned} \end{gather} $$

CMRR

$$ \begin{gather} \begin{aligned} CMMR &= \frac{ R_1 }{ \Delta } \end{aligned} \end{gather} $$

Noise & Opamp

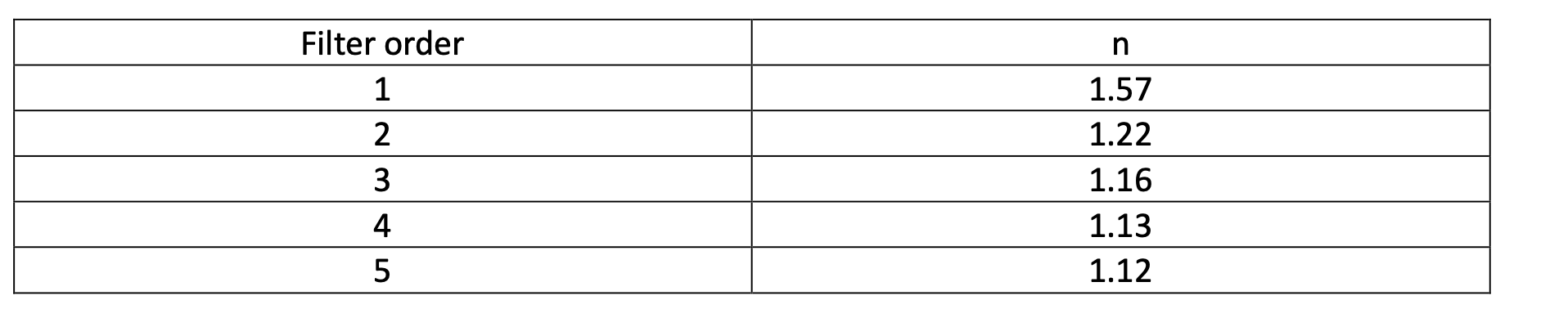

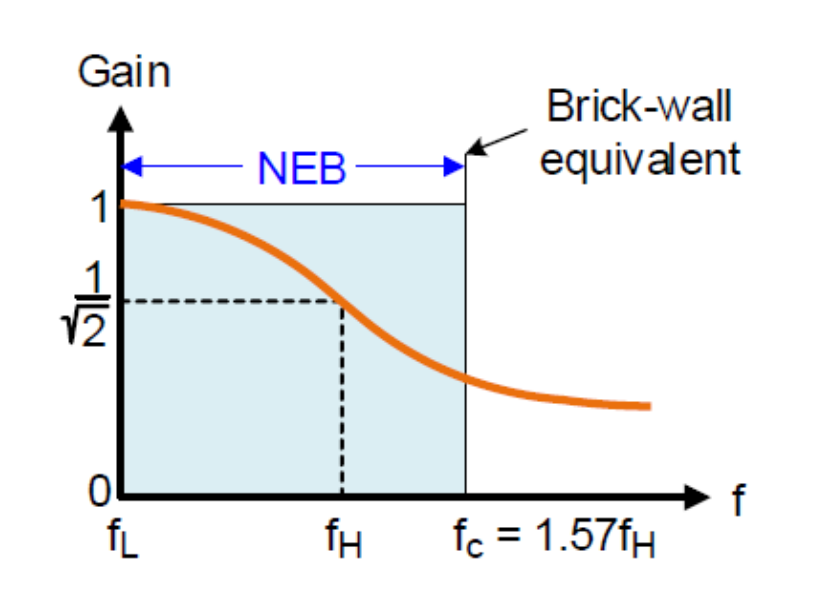

SNR & NEB

- Signal to Noise Ratio (SNR) and Noise Equivalent Bandwidth (NEB)

$$ \begin{gather} \begin{aligned} SNR &= 20 \times lg( \frac{ V_s(rms) }{ V_n(rms) }) \end{aligned} \end{gather} $$

$$ \begin{gather} \begin{aligned} NEB &= n \times \frac{ GBW }{ Noise \ Gain } \end{aligned} \end{gather} $$

- n is Brick-Wall Factor

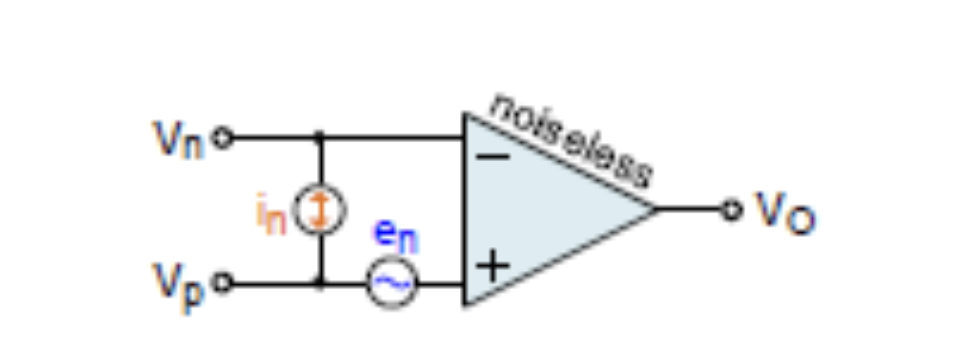

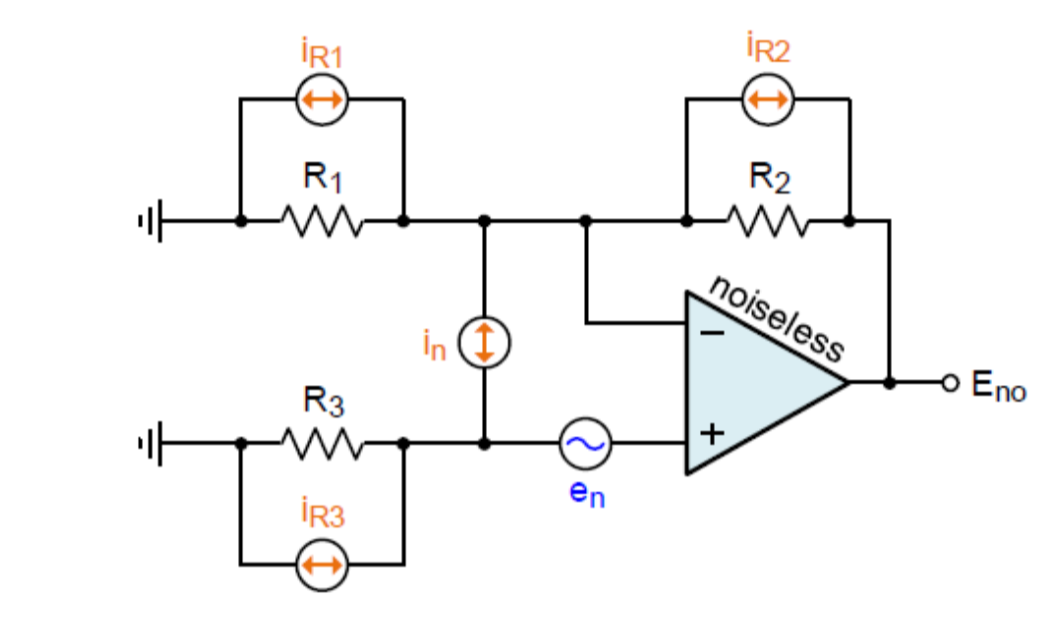

Opamp Noise Model

Circuit

- $i_n, e_n$ are Spectral Density

White Noise Passing LPF

RMS Input Noise

Formulas

- $R_1 || R_2 = R_3$

$$ \begin{gather} \begin{aligned} E_{R1-R2} &= E_{RP} = \sqrt{ 4kT \times 1.57 f_H \times (R_1 || R_2)} \\ E_{R3} &= E_{RP} \\ E_{nn} &= i_n (R_1 || R_2) \sqrt{ 1.57 f_H } \\ E_{np} &= E_{nn} \\ E_{n} &= e_n \sqrt{ 1.57 f_H } \\ E_{ni} &= \sqrt{ E_{R1 -R2}^2 + E_{R3}^2 + E_{nn}^2 + E_{np}^2 + E_n^2} \\ &= \sqrt{ 1.57 f_H} \sqrt{ 8kTR_P + 2R_P^2 i_n^2 + e_n^2 } \end{aligned} \end{gather} $$

- $E_{ni}$ refers to the non-inverting input

$$ \begin{gather} \begin{aligned} E_{noise} &= E_{ni} (1 + \frac{ R_2 }{ R_1 }) \end{aligned} \end{gather} $$

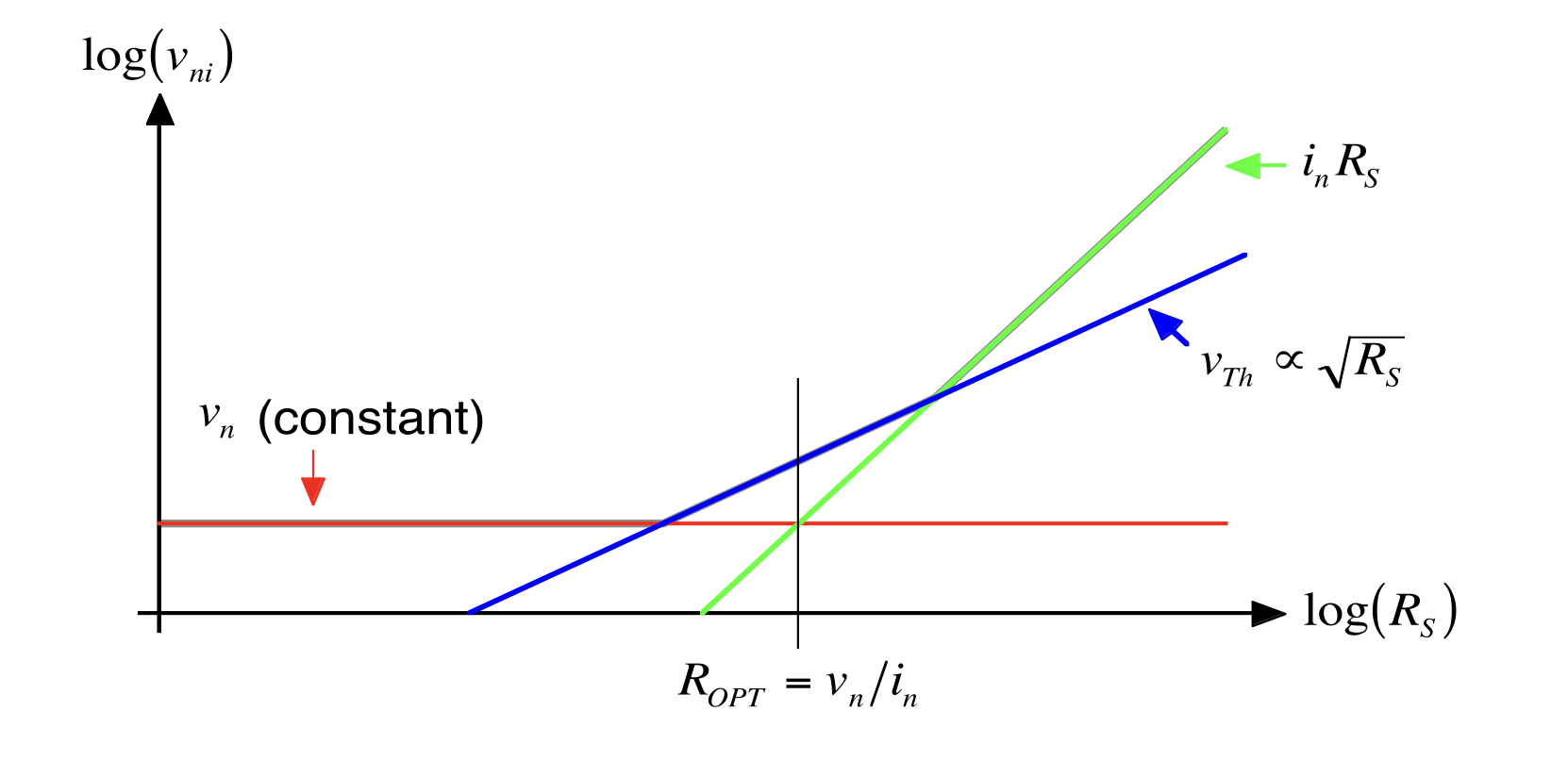

Relationship in Graph

Appendix

CheckList

| Category | Concept |

|---|---|

| 什么情况下使用Bias 或 Offset | Impedance (Very) Unbalanced: Bias; Impedance Matched: Offset |

| Figure of Merit | A function of all significant contributions of the components to the total system error, which changes monotonically with the overall error |

| Shielding | Covering it with Metal |

| twisted pair | 减少Differential Noise |

| Supply Decoupling | 对于大电流电路端,需要单独使用宽轨线进行布线, 防止磁场干扰、过热、噪声问题 |

| Ground Bounce | 多个芯片共享参考地,产生回路电流干扰和寄生电容、电感 |

| Supply Decoupling | 在供电引脚之间防止无极性电容(去耦电容), 隔离噪声干扰 |

| Cold End | 连接Load和Ground的电路 |

| Hot End | 连接Power和Input Signal的电路 |

| Thermocouple | 两种不同材料的导线连在一起,当有$\Delta T$时,就会产生电动势 |

| White Noise | Noise that has flat Spectral Density |

| 3 Sources for Noise | 两个Voltage Inputs, 每个输入端的Current Noise |

| 2 Reasons for Noise | Recombination & Generation of electrons in semiconductors; Thermal Agitation of electrons, $E_r = \sqrt{4 R k T \Delta f}$, $\Delta f$ is bandwidth |

| Noise Equivalent Bandwidth | 在指定带宽内,能产生和实际噪声功率相等的均匀白噪声所对应的等效宽带 |

| Gain-Bandwdith | The point of Unitary-Gain, 能够提供一定增益的最大频率带宽 |

公式

- Dynamic Range (DR)

$$ \begin{gather} \begin{aligned} DR &= 20 \times lg( \frac{ V_{max} }{ V_{min} }) \\ &= (6.02N + 1.76) dB \end{aligned} \end{gather} $$

- Energy Spectral Density

$$ \begin{gather} \begin{aligned} V &= \sqrt{ E_n \Delta f } \end{aligned} \end{gather} $$