Transistor

| Category | Concept |

|---|---|

| 栅宽$W$ | $W$越大, 饱和输出功率$P_{Sout}$越大,增益$G$越小 |

| 栅指宽度$w$ | $w$越大,越不利于散热 |

| 栅指数量$N$ | $N$越大,寄生参数越大,阻抗减小,不利于匹配 |

| 功率密度$\rho_P (mW/mm)$ | $\rho_P$是该功率下的最小栅宽总和,否则有负载风险 |

| 工艺角 | tt(Typical Corner), ff(Fast Corner),时间增长,功率下降 ss(Slow Corner), 时间减短,功率增高 |

Layout

| Category | Concept |

|---|---|

| PO | Poly(多晶硅)层 |

| OD | Oxide Diffusion, 有源层 |

| CO | Contact, 金属接触层 |

| CBM | Capacitor Bottom Metal |

| CTM | Capacitor Top Metal |

PA 设计经验

小总结

-

相邻走线可以交替M8, M9, 避免耦合|

-

连接晶体管的走线一定不要靠在一起!

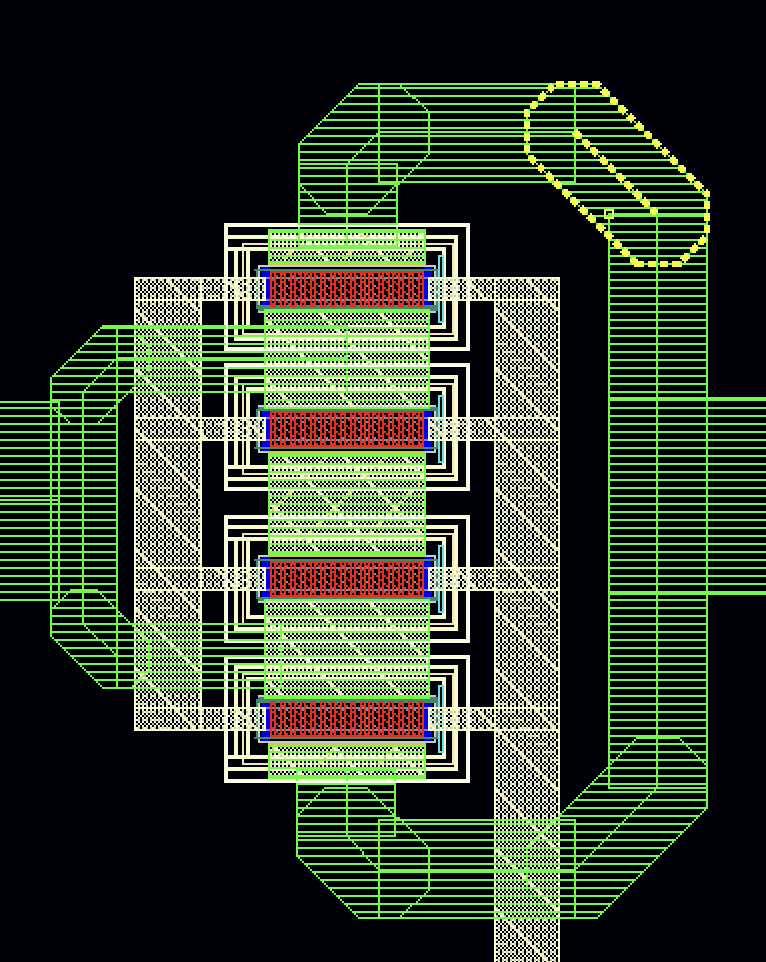

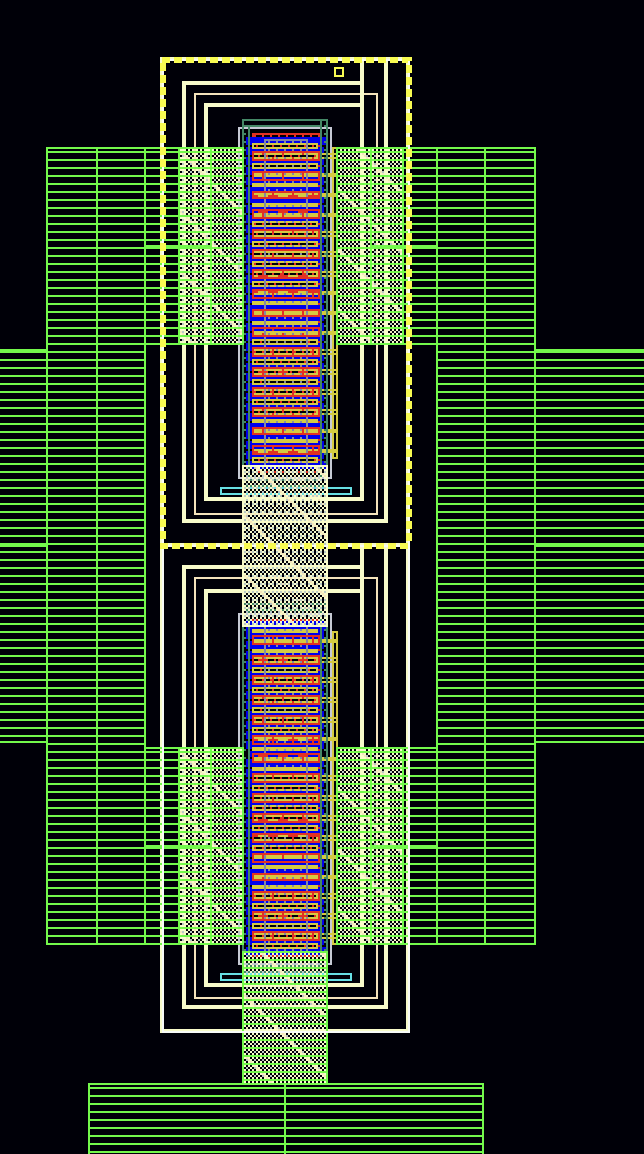

晶体管版图连接

两个晶体管并联

四个晶体管并联